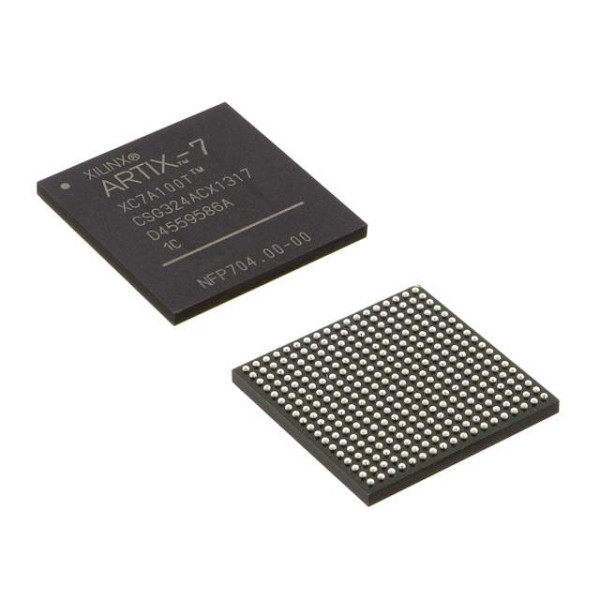

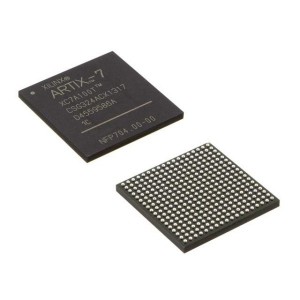

XC7A50T-2CSG324I FPGA – Arae Giât Rhaglenadwy Maes XC7A50T-2CSG324I

♠ Disgrifiad o'r Cynnyrch

| Priodoledd Cynnyrch | Gwerth Priodoledd |

| Gwneuthurwr: | Xilinx |

| Categori Cynnyrch: | FPGA - Arae Giât Rhaglenadwy Maes |

| Cyfres: | XC7A50T |

| Nifer yr Elfennau Rhesymeg: | 52160 LE |

| Nifer yr Mewnbwn/Os: | 210 Mewnbwn/Allbwn |

| Foltedd Cyflenwad - Isafswm: | 0.95 V |

| Foltedd Cyflenwad - Uchafswm: | 1.05 V |

| Tymheredd Gweithredu Isafswm: | - 40 gradd Celsius |

| Tymheredd Gweithredu Uchaf: | + 100°C |

| Cyfradd Data: | - |

| Nifer y Trawsyrwyr: | - |

| Arddull Mowntio: | SMD/SMT |

| Pecyn / Achos: | CSBGA-324 |

| Brand: | Xilinx |

| RAM wedi'i ddosbarthu: | 600 kbit |

| RAM Bloc Mewnosodedig - EBR: | 2700 kbit |

| Lleithder Sensitif: | Ie |

| Nifer y Blociau Arae Rhesymeg - LABs: | 4075 LAB |

| Foltedd Cyflenwad Gweithredu: | 1 V |

| Math o Gynnyrch: | FPGA - Arae Giât Rhaglenadwy Maes |

| Nifer y Pecyn Ffatri: | 1 |

| Is-gategori: | ICs Rhesymeg Rhaglenadwy |

| Enw masnach: | Artix |

| Pwysau'r Uned: | 1 owns |

♠ Mae FPGAau cyfres Xilinx® 7 yn cynnwys pedwar teulu FPGA sy'n mynd i'r afael â'r ystod gyflawn o ofynion system, yn amrywio o gymwysiadau cost isel, ffactor ffurf bach, sensitif i gost, cyfaint uchel i led band cysylltedd pen uchel iawn, capasiti rhesymeg, a gallu prosesu signal ar gyfer y cymwysiadau perfformiad uchel mwyaf heriol

Mae FPGAau cyfres 7 Xilinx® yn cynnwys pedwar teulu FPGA sy'n mynd i'r afael â'r ystod gyflawn o ofynion system, yn amrywio o gymwysiadau cost isel, ffactor ffurf bach, sensitif i gost, cyfaint uchel i led band cysylltedd pen uchel iawn, capasiti rhesymeg, a gallu prosesu signal ar gyfer y cymwysiadau perfformiad uchel mwyaf heriol. Mae'r FPGAau cyfres 7 yn cynnwys:

• Teulu Spartan®-7: Wedi'i optimeiddio ar gyfer cost isel, y pŵer isaf, a pherfformiad I/O uchel. Ar gael mewn pecynnu ffactor ffurf bach iawn, cost isel ar gyfer ôl troed PCB lleiaf.

• Teulu Artix®-7: Wedi'i optimeiddio ar gyfer cymwysiadau pŵer isel sy'n gofyn am draws-dderbynyddion cyfresol a thryloywder DSP a rhesymeg uchel. Yn darparu'r gost bil deunyddiau gyfan isaf ar gyfer cymwysiadau tryloywder uchel sy'n sensitif i gost.

• Teulu Kintex®-7: Wedi'i optimeiddio ar gyfer y pris-perfformiad gorau gyda gwelliant 2x o'i gymharu â'r genhedlaeth flaenorol, gan alluogi dosbarth newydd o FPGAs.

• Teulu Virtex®-7: Wedi'i optimeiddio ar gyfer y perfformiad a'r capasiti system uchaf gyda gwelliant 2x mewn perfformiad system. Dyfeisiau â'r gallu uchaf wedi'u galluogi gan dechnoleg rhyng-gysylltu silicon wedi'i stacio (SSI).

Wedi'i adeiladu ar dechnoleg prosesu giât fetel k uchel (HKMG) 28 nm, perfformiad uchel, pŵer isel (HPL) o'r radd flaenaf, mae FPGAs cyfres 7 yn galluogi cynnydd digyffelyb mewn perfformiad system gyda lled band I/O o 2.9 Tb/s, capasiti 2 filiwn o gelloedd rhesymeg, a DSP o 5.3 TMAC/s, wrth ddefnyddio 50% yn llai o bŵer na dyfeisiau cenhedlaeth flaenorol i gynnig dewis arall cwbl raglenadwy i ASSPs ac ASICs.

• Rhesymeg FPGA perfformiad uchel uwch yn seiliedig ar dechnoleg tabl chwilio 6-mewnbwn (LUT) go iawn y gellir ei ffurfweddu fel cof dosbarthedig.

• RAM bloc deuol-borth 36 Kb gyda rhesymeg FIFO adeiledig ar gyfer byffro data ar y sglodion.

• Technoleg SelectIO™ perfformiad uchel gyda chefnogaeth ar gyfer rhyngwynebau DDR3 hyd at 1,866 Mb/s.

• Cysylltedd cyfresol cyflym gyda thrawsyrwyr aml-gigabit adeiledig o 600 Mb/s i gyfraddau uchaf o 6.6 Gb/s hyd at 28.05 Gb/s, gan gynnig modd pŵer isel arbennig, wedi'i optimeiddio ar gyfer rhyngwynebau sglodion-i-sglodion.

• Rhyngwyneb analog y gellir ei ffurfweddu gan y defnyddiwr (XADC), sy'n ymgorffori trawsnewidyddion analog-i-ddigidol deuol 12-bit 1MSPS gyda synwyryddion thermol a chyflenwad ar y sglodion.

• Sleisys DSP gyda lluosydd 25 x 18, cronnwr 48-bit, a rhag-ychwanegwr ar gyfer hidlo perfformiad uchel, gan gynnwys hidlo cyfernod cymesur wedi'i optimeiddio.

• Teils rheoli cloc pwerus (CMT), gan gyfuno blociau dolen glo-gyfnod (PLL) a rheolwr cloc modd cymysg (MMCM) ar gyfer cywirdeb uchel a jitter isel.

• Defnyddio prosesu mewnosodedig yn gyflym gyda phrosesydd MicroBlaze™.

• Bloc integredig ar gyfer PCI Express® (PCIe), ar gyfer dyluniadau Pwynt Terfynol a Phorthladd Gwraidd Gen3 hyd at x8.

• Amrywiaeth eang o opsiynau ffurfweddu, gan gynnwys cefnogaeth ar gyfer cofion nwyddau, amgryptio AES 256-bit gyda dilysiad HMAC/SHA-256, a chanfod a chywiro SEU adeiledig.

• Pecynnu fflip-sglodion cost isel, bond gwifren, marw noeth, a chyfanrwydd signal uchel sy'n cynnig mudo hawdd rhwng aelodau'r teulu yn yr un pecyn. Mae pob pecyn ar gael mewn pecynnau di-blynedd a phecynnau dethol mewn opsiwn blynedd.

• Wedi'i gynllunio ar gyfer perfformiad uchel a'r pŵer isaf gyda 28 nm, HKMG, proses HPL, technoleg proses foltedd craidd 1.0V ac opsiwn foltedd craidd 0.9V ar gyfer pŵer hyd yn oed yn is.